**JW7952**

20W Full-Bridge with Demodulation and LDO for the Wireless Charger Transmitter

Preliminary Specifications Subject to Change without Notice

# **DESCRIPTION**

The JW7952 is a high efficiency full-bridge power stage with voltage/current demodulation designed for wireless charger transmitter. With a transmitter controller, it can provide flexible wireless charger solutions complaint with Qi v1.2.4 and Qi v1.3 Baseline Power Profile (BPP) and Extended Power Profile (EPP).

The JW7952 integrates a 4-MOSFETs full bridge with low R<sub>DS(ON)</sub>, gate drivers, 5V LDO, 3.3V LDO, current sensor voltage/current communication demodulation, Q factor detection and protection circuit.

The JW7952 provides input current sense function. The chip measures the input current with the current sampling resistor and reports it on the CSO pin, so that the transferred power can be detected by the controller. The controller realizes foreign object detection (FOD) by continuously monitoring transferred power and received power. For EPP equipment, Q factor detection is required to realize foreign object protection by comparing with the set Q threshold.

The JW7952 guarantees robustness with under voltage lockout (UVLO), input over voltage protection(OVLO), over current protection (OCP) and thermal shutdown(OTP).

Company's Logo is Protected, "JW" and "JOULWATT" are Registered

Trademarks of Joulwatt Technology Co., Ltd.

# **FEATURES**

- Full Bridge Input Voltage Range: 2V~14V

- LDO Input Voltage Range: 2.8V~20V

- Output power: 20W

- Integrated Four Low  $R_{DS(ON)}$  FETs :  $12m\Omega$

- Integrated 5V/50mA LDO

- Integrated 3.3V/50mA LDO

- 3.3V and 5V PWM Signal Logic Compatible

- Integrated voltage and current demodulation

- Integrated input current sense for FOD

- Integrated Q factor detection for QFOD

- Under Voltage Lockout (UVLO)

- Input Over Voltage Protection(OVLO) lacktrian

- Over Current Protection(OCP)

- Thermal Shutdown(OTP)

- RoHS Compliant and Halogen Free

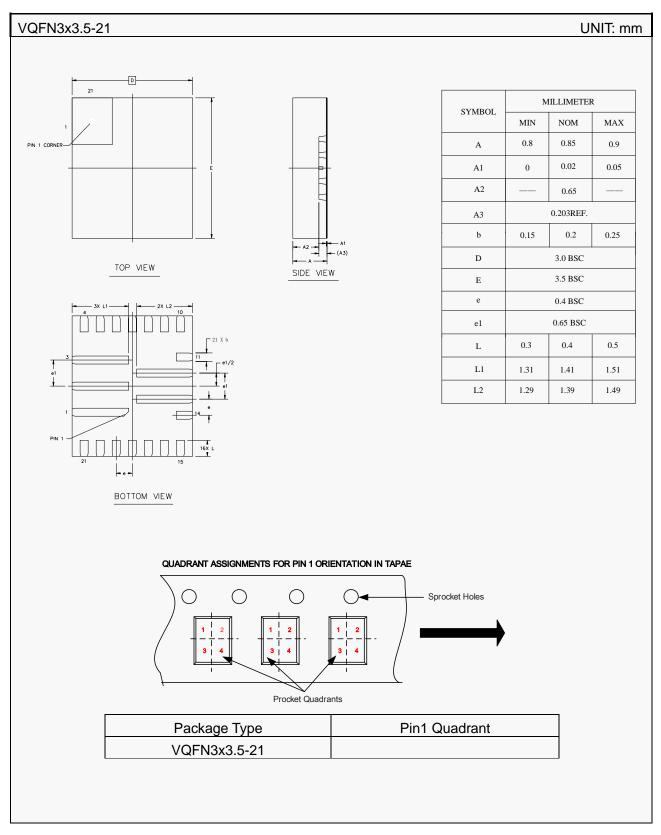

- Compact Package: VQFN3x3.5-21

# **APPLICATIONS**

- Wireless Charger Transmitter

- Motor Drivers

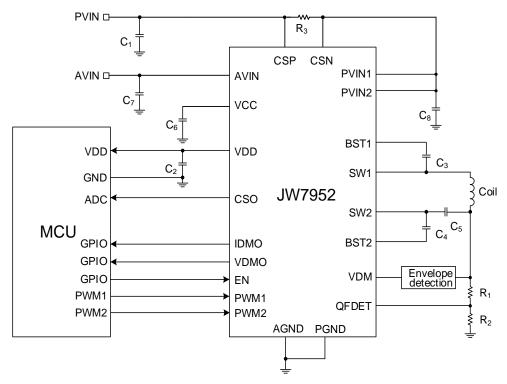

# **TYPICAL APPLICATION**

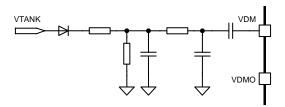

Typical application circuit

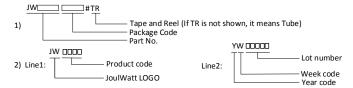

# ORDER INFORMATION

| DEVICE <sup>1)</sup> | PACKAGE      | TOP MARKING <sup>2)</sup> | ENVIRONMENTAL <sup>3)</sup> |

|----------------------|--------------|---------------------------|-----------------------------|

| JW7952VQBFX#TR       | VQFN3x3.5-21 | JW7952<br>YWnnnn          | Green                       |

#### Notes:

3) All Joul Watt products are packaged with Pb-free and Halogen-free materials and compliant to RoHS standards.

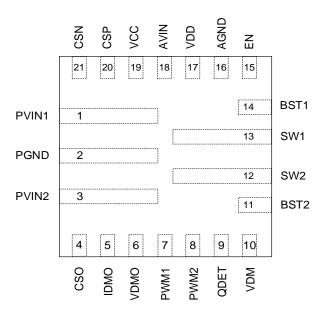

# **PIN CONFIGURATION**

### **TOP VIEW**

**VQFN3×3.5-21**

# ABSOLUTE MAXIMUM RATING1)

| PVIN1, PVIN2, SW1,SW2, CSP, CSN | 0.3V to 16.5V |

|---------------------------------|---------------|

| AVIN                            | 0.3V to 22V   |

| BST1-SW1, BST2-SW2              | 0.3V to 4V    |

| PWM1, PWM2, VDMO, IDMO, EN, VDD | 0.3V to 6.5V  |

| CSO, QDET, VCC,VDM              | 0.3V to 4V    |

JW7952 Rev.0.11 2023/07/10 JoulWatt Proprietary Information. Patent Protected.

Unauthorized Photocopy and Duplication Prohibited.

3/15

This document contains information of a product under development.

JoulWatt

| Junction Temperature Range <sup>2)</sup>                                    | 40°C to +150°C                                                         |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|

| Power Dissipation, P <sub>D</sub> @ (T <sub>A</sub> = 25°C) 3) VQFN3×3.5-21 | TBD                                                                    |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C                                                                  |

| Storage Temperature Range                                                   | 65°C to +150°C                                                         |

| Human-body model(HBM)                                                       | ±2kV                                                                   |

| Charged device model(CDM),per JEDEC specification JESD22-C101               | ±500V                                                                  |

| RECOMMENDED OPERATING CONDITIONS <sup>4)</sup>                              |                                                                        |

| AVIN                                                                        | 2.8V to 20V                                                            |

| PVIN                                                                        | 2V to 14V                                                              |

| Junction Temperature Range                                                  |                                                                        |

| Ambient Temperature Range                                                   | 40°C to +85°C                                                          |

| THERMAL PERFORMANCE <sup>5)</sup>                                           | $	heta_{\!\scriptscriptstyle J\!A}  	heta_{\!\scriptscriptstyle J\!C}$ |

| VQFN3×3.5-21                                                                | °C/W                                                                   |

# Note:

- 1) Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDED OPERATIONF CONDITIONS

- 2) The JW7952 includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) =  $(T_J(MAX)-T_A)/\theta_{JA}$ .

- 4) The device is not guaranteed to function outside of its operating conditions.

- **5)** Measured in the natural convection at  $T_A = 25\,^{\circ}\mathbb{C}$  on the JoulWatt Evaluation Board.

# **ELECTRICAL CHARACTERISTICS**

$V_{AVIN}$ =12V,  $T_A$ =25°C, unless otherwise specified.

Advance Information, not production data, subject to change without notice.

| Item                                  | Symbol                 | Condition                                                                               | Min.  | Тур.  | Max.  | Uni<br>ts |

|---------------------------------------|------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-----------|

| POWER SUPPLY                          |                        |                                                                                         |       |       |       |           |

| LDO Operating Input Voltage           | V <sub>AVIN</sub>      |                                                                                         | 2.8   |       | 20    | V         |

| Full-Bridge Operating Input Voltage   | V <sub>PVIN</sub>      |                                                                                         | 2     |       | 14    | V         |

| AVIN Under Voltage Lockout Threshold  | Vavin_uvlo             | V <sub>AVIN</sub> rising                                                                |       | 2.73  |       | V         |

| AVIN Under Voltage Lockout Hysteresis | Vavin_HYS              |                                                                                         |       | 203   |       | mV        |

| PVIN Over Voltage Lockout Threshold   | V <sub>PVIN_OVLO</sub> | V <sub>PVIN</sub> rising                                                                |       | 16    |       | V         |

| PVIN Over Voltage Lockout Hysteresis  | V <sub>PVIN_HYS</sub>  |                                                                                         |       | 0.824 |       | V         |

| VCC UVLO Threshold                    | V <sub>VCC_UVLO</sub>  | V <sub>CC</sub> rising                                                                  |       | 2.62  |       | V         |

| VCC UVLO Hysteresis                   | Vvcc_hys               |                                                                                         |       | 209   |       | mV        |

| Quiescent Current from AVIN Pin       | I <sub>Q_AVIN</sub>    | VCC,VDD no Load                                                                         |       | 534   |       | uA        |

| Quiescent Current from PVIN1, PVIN2   | I <sub>Q_PVIN</sub>    | EN=high,no switch                                                                       |       | 15.7  |       | uA        |

| Shutdown Current from AVIN Pin        | Ishdn_avin             | EN=low, V <sub>AVIN</sub> =12V                                                          |       | 90.1  |       | uA        |

| Shutdown Current from PVIN1, PVIN2    | I <sub>SHDN_PVIN</sub> | EN=low, V <sub>PVIN1</sub> =12V                                                         |       | 0.15  | 3     | uA        |

| FULL BRIDGE POWER STAGE               |                        |                                                                                         |       |       |       |           |

| High Side N-FET(LS-FET) Ron           | R <sub>DS(ON)_</sub> H | V <sub>BST1</sub> -V <sub>SW1</sub> =3.3V,<br>V <sub>BST2</sub> -V <sub>SW2</sub> =3.3V |       | 12    |       | mΩ        |

| Low Side N-FET(HS-FET) Ron            | R <sub>DS(ON)_L</sub>  | Vcc=3.3V                                                                                |       | 12    |       | mΩ        |

| Switch Minimum off Time               | T <sub>off_min</sub>   |                                                                                         |       | 120   |       | ns        |

| Switch Minimum on Time                | T <sub>on_min</sub>    |                                                                                         |       | 120   |       | ns        |

| How Side Current Limit Threshold      | I <sub>LIM</sub>       |                                                                                         |       | 12.95 |       | Α         |

| Hiccup Period                         | Тр                     |                                                                                         |       | 20    |       | ms        |

| LDO OUTPUT                            |                        |                                                                                         |       |       |       |           |

| VCC Output Voltage                    | Vcc                    | V <sub>AVIN</sub> =12V,<br>I <sub>VCC</sub> =10mA                                       | 3.24  | 3.3   | 3.37  | V         |

| VCC Current Limit                     | I <sub>VCC_LIM</sub>   |                                                                                         |       | 62    |       | mA        |

| VCC Short Current                     | I <sub>vcc_sc</sub>    |                                                                                         |       | 21    |       | mA        |

| VDD Output Voltage                    | V <sub>DD</sub>        | V <sub>AVIN</sub> =12V,<br>I <sub>VDD</sub> =10mA                                       | 4.92  | 5     | 5.13  | \<br>\    |

| VDD Current Limit                     | IVDD_LIM               |                                                                                         |       | 62    |       | mA        |

| VDD Short Current                     | I <sub>VDD_SC</sub>    |                                                                                         |       | 21    |       | mA        |

| CURRENT SENSE                         |                        |                                                                                         |       |       |       |           |

| CSO Current Sense Ratio               | Rcs_Gain               | R <sub>CS</sub> =10mΩ                                                                   | 0.497 | 0.5   | 0.502 | V/A       |

| CSO Current Sense Offset              | Vcs_Offset             | I <sub>PVIN</sub> =0A                                                                   |       | 0.51  |       | V         |

| DEMODULATION                                   |                         |                                                          |         |     |         |    |

|------------------------------------------------|-------------------------|----------------------------------------------------------|---------|-----|---------|----|

| VDM Input Hysteresis Voltage                   | V <sub>VDM_HYS</sub>    |                                                          |         | 22  |         | mV |

| IDM Input Hysteresis Voltage                   | V <sub>IDM_HYS</sub>    |                                                          |         | 14  |         | mV |

| Q FACTOR DETECTION                             |                         |                                                          |         |     |         |    |

| Preset Voltage Threshold on SW1                | V <sub>TH_PRESET</sub>  |                                                          |         | 2.5 |         | V  |

| High Level Detect Voltage Threshold            | V <sub>TH_</sub> HIGH   |                                                          |         | 200 |         | mV |

| Low Level Detect Voltage Threshold             | V <sub>TH_LOW</sub>     |                                                          |         | 100 |         | mV |

| TIMING                                         |                         |                                                          |         |     |         |    |

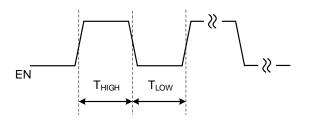

| High-level Pulse Duration <sup>(6)</sup>       | T <sub>HIGH</sub>       |                                                          |         | 10  |         | us |

| Low-level Pulse Duration <sup>(6)</sup>        | T <sub>LOW</sub>        |                                                          |         | 10  |         | us |

| Turn-off Delay Time <sup>(6)</sup>             | T <sub>D(OFF)</sub>     |                                                          |         | 80  |         | us |

| Data Storage/Accept Time Period <sup>(6)</sup> | TSTORE                  |                                                          | 50      |     |         | us |

| LOGIC INTERFACE                                |                         |                                                          |         |     |         |    |

| PWM1, PWM2 Logic High Threshold                | V <sub>PWM_</sub> H     | Vcc=3.3V,VDD=5V, Input Rising                            | 2       |     |         | ٧  |

| PWM1, PWM2 Logic Low Threshold                 | V <sub>PWM_L</sub>      | Vcc=3.3V,VDD=5V, Input Falling                           |         |     | 0.8     | V  |

| EN Logic High Threshold                        | V <sub>EN_</sub> H      | V <sub>CC</sub> =3.3V,V <sub>DD</sub> =5V,<br>EN Rising  | 2       |     |         | V  |

| EN Logic Low Threshold                         | V <sub>EN_L</sub>       | V <sub>CC</sub> =3.3V,V <sub>DD</sub> =5V,<br>EN Falling |         |     | 0.8     | V  |

| VDMO,IDMO Output Logic High                    | V <sub>DMO_H_</sub> vdd | EN Rising Edges<br>19/0                                  | 0.9*VDD |     |         | ٧  |

| VDMO,IDMO Output Logic Low                     | $V_{DMO\_L\_VDD}$       | EN Rising Edges<br>19/0                                  |         |     | 0.1*VDD | ٧  |

| VDMO,IDMO Output Logic High                    | V <sub>DMO_H_VCC</sub>  | EN Rising Edges 18                                       | 0.9*VCC |     |         | V  |

| VDMO,IDMO Output Logic Low                     | V <sub>DMO_L_VCC</sub>  | EN Rising Edges 18                                       |         |     | 0.1*VCC | V  |

| PROTECTION                                     |                         |                                                          |         |     |         |    |

| Thermal Shutdown Temperature <sup>(6)</sup>    | T <sub>SD</sub>         |                                                          |         | 155 |         | °C |

| Thermal Shutdown Hysteresis <sup>(6)</sup>     | T <sub>HYS</sub>        |                                                          |         | 15  |         | °C |

# Note:

6) Guaranteed by design.

# **PIN DESCRIPTION**

| Pin No. | Name  | Description                                                                                                                                                                                                                          |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PVIN1 | Input voltage for half-bridge MOSFET. Bypass with a 22 $\mu\text{F}$ ceramic capacitor to PGND.                                                                                                                                      |

| 2       | PGND  | Power ground.                                                                                                                                                                                                                        |

| 3       | PVIN2 | Input voltage for half-bridge MOSFET. Bypass with a 22 $\mu\text{F}$ ceramic capacitor to PGND.                                                                                                                                      |

| 4       | cso   | Input current sense output pin.                                                                                                                                                                                                      |

| 5       | IDMO  | Output of the demodulated 2-kHz communication signal based on current demodulation scheme.                                                                                                                                           |

| 6       | VDMO  | Output of the demodulated 2-kHz communication signal based on voltage demodulation scheme.                                                                                                                                           |

| 7       | PWM1  | PWM input for the control of the arm at SW1 side. When PWM1 is high, the top switch Q1 is turned on and the bottom switch Q2 is turned off. When PWM1 is low, the top switch Q1 is turned off and the bottom switch Q2 is turned on. |

| 8       | PWM2  | PWM input for the control of the arm at SW2 side. When PWM2 is high, the top switch Q4 is turned on and the bottom switch Q3 is turned off. When PWM2 is low, the top switch Q4 is turned off and the bottom switch Q3 is turned on. |

| 9       | QDET  | Quality factor detection input.                                                                                                                                                                                                      |

| 10      | VDM   | High-pass filter input. Voltage demodulation pin for data packets based on coil voltage variation.                                                                                                                                   |

| 11      | BST2  | Bootstrapped supplies to the high side floating driver of Q4. An 0.1µF ceramic capacitor is suggested to be connected between this pin and SW2 pin.                                                                                  |

| 12      | SW2   | Power switching node 2.                                                                                                                                                                                                              |

| 13      | SW1   | Power switching node 1.                                                                                                                                                                                                              |

| 14      | BST1  | Bootstrapped supplies to the high side floating driver of Q1. An 0.1µF ceramic capacitor is suggested to be connected between this pin and SW1 pin.                                                                                  |

| 15      | EN    | Chip enable pin. Active High to enable the chip. When EN is low, the chip is disabled, and both SW1 and SW2 are pulled down to PGND for about 200us, and then change to high-Z.                                                      |

| 16      | AGND  | Analog Ground.                                                                                                                                                                                                                       |

| 17      | VDD   | 5.0V LDO for internal circuits and external MCU. Connect a 2.2 µF ceramic capacitor from VDD to AGND.                                                                                                                                |

| 18      | AVIN  | Input voltage for internal 5.0V LDO and 3.3V LDO, Bypass with a 10 $\mu F$ ceramic capacitor to AGND.                                                                                                                                |

| 19 | VCC | 3.3V LDO for internal gate drivers ,control circuits and external MCU. Connect a 2.2 µF ceramic capacitor from VCC to AGND. |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------|

| 20 | CSP | Positive terminal of input current sense.                                                                                   |

| 21 | CSN | Negative terminal of input current sense.                                                                                   |

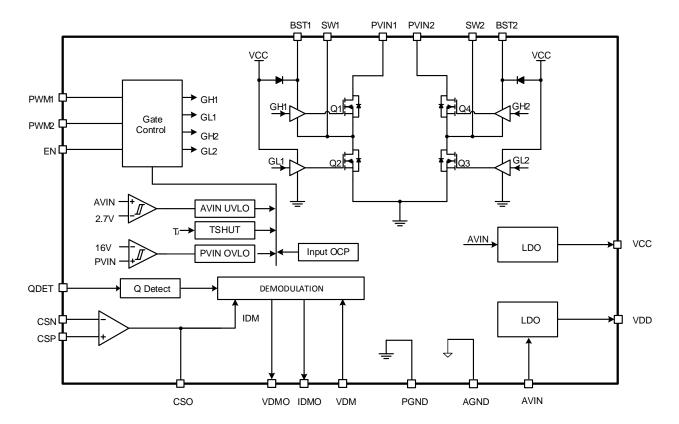

# **BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTION**

JW7952 is a high-efficiency full-bridge power stage (integrated MOS plus driver) with voltage/current demodulation and LDO for wireless charger transmitter. With a transmitter controller, it can provide flexible wireless transmitter solutions, compliant with Qi v1.2.4 and Qi v1.3 Baseline Power Profile and Extended Power Profile.

# **Integrated Full-Bridge Stage**

The JW7952 integrates a full-bridge power stage with low  $R_{DSON}$  (typical  $12m\Omega$ ) N-channel MOSFETs and can work with wide input voltage ranging from 1.0V to 14V. All circuits needed to drive the full-bridge stage are integrated, such as gate driver and bootstrap circuits. With the PWM control signals from the controller, it can be widely used in wireless transmitter applications.

#### **PWM Control**

The JW7952 has two PWM input pins, PWM1 and PWM2. Each input signal can control one arm of the integrated full-bridge independently. The PWM1 input controls the arm of Q1 and Q2, and the PWM2 input controls the arm of Q3 and Q4.

When the input PWM signal is high, the top switch of the corresponding arm is turned on, and the bottom switch of this arm is turned off. When the input PWM signal is low, the bottom switch of the corresponding arm is turned on, and the bottom switch is turned off. For example, when PWM1 is high, the Q1 is turned on and Q2 is turned off. When PWM1 is low the Q1 is turned off and Q2 is turned on.

For a typical WPC transmitter, the PWM1 and PWM2 are complementary and the duty cycle is fixed in 50% with the frequency range from

100kHz to 205kHz. When the frequency reaches 205kHz, the output power can be limited furtherly by reducing the duty cycle of PWM1 and PWM2.

#### **Current Sense**

The JW7952 provides input current sense function. The total input current is measured by the current sensing resistor and reported on CSO pin.

The integrated current sense amplifier has voltage gain of 50 V/V. For proper scaling of the current signal, the recommended current sense resistor is  $10m\Omega/20m\Omega$ . The current sense amplifier output has a fixed 0.5V (typical) offset when the sensed current is zero. For accurate measurement of the input current, MCU need to calibrate this offset.

The output voltage of CSO pin can be calculated by the formula below.

$$V_{CSO}(V) = 0.5V + R_{CS}(\Omega) \times 50 \times I_{PVIN}(A)$$

#### **LDO**

The JW7952 has two integrated low-dropout (LDO) voltage regulators. VCC pin is 3.3V LDO output and VDD pin is 5V LDO output. The internal power drivers and control circuits are powered from the VCC. The load capability of VDD/VCC regulator is about 50mA, so it can be used to power up MCU and LED directly. Customers can choose to use 3.3V or 5V power supply according to the application.

The VCC and VDD regulator is not controlled by the EN signal.

# **Voltage Demodulation**

In order to increase the communication reliability in any load condition, the JW7952 has integrated

two demodulation schemes, one based on input average current information and the other based on coil voltage information. The voltage mode envelope detector is implemented using a discrete solution as depicted on Figure 1. This simple implementation achieves the envelope detector function low-pass filter as well as the DC filter function.

Figure 1. Voltage Demodulation peripheral circuit

#### **Current Demodulation**

The current-mode detector takes the modulation information from the average input current. The input signal of current demodulation is CSO pin. The 2KHz data signal carried by the input current is demodulated through the internal current demodulation circuit.

The MCU can detect the demodulation results on VDMO and IDMO pins and then implement the packet decode. The MCU can select either voltage-mode or current-mode signals depending upon which produces the best demodulated signal.

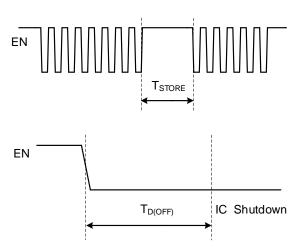

#### **Q Factor Detection**

The JW7952 integrates an accurate Q factor detection circuit to implement foreign objects detection before the selection phase. When a metal foreign object is placed on the charging surface of Tx, the quality factor of the resonant circuit composed of coil, resonant capacitance and parasitic resistance will decrease. Set a reasonable quality factor threshold to judge whether there is metal foreign matter on the surface of the coil.

After Q detection is enabled, MCU can calculate the Q of TX according to the number of pulses on VDMO pin, and then judge whether there is metal foreign objects on the charging surface of  $T_X$  before the selection stage.

The calculation formula of Q value is as follows.

Figure 2. Q Factor detection diagram

# Digital Interface (EN pin)

The digital interface is used to Q factor detection function. If digital interface is not required, the EN pin can also be used as a standard enable pin. Once the device is enabled, Q factor detection is not implemented. The interface counts the rising edges applied to the EN pin and enable the new function according to Table 1.

Table 1 Programming Table

| Rising Edges | Function                  |

|--------------|---------------------------|

| 13           | Enable Q factor detection |

| 0/14 | Disable Q factor detection             |

|------|----------------------------------------|

| 15   | Driver speed slowest                   |

| 16   | Driver speed slow                      |

| 0/17 | Driver speed fast                      |

| 18   | Set the VDMO/IDMO logic voltage to VCC |

| 0/19 | Set the VDMO/IDMO logic voltage to VDD |

In order to realize the digital interface function of EN pin, the high level and the low level between two adjacent rising edges need to keep for  $T_{HIGH}(Typ.~10us)$  and  $T_{LOW}(Typ.~10us)$ .

After the EN pulses, the high level shall be maintained at least  $T_{STORE}$  (Min. 50us) to enable the corresponding function. At the same time, the rising edge counter is set to 0, and EN can continue to pulse to enable the next function. That is, between the enabling of the two functions, the EN shall keep high level for least  $T_{STORE}$  (Min. 50us).

After the EN remains low level for  $T_{D(OFF)}$  (Typ 80us), the chip will shut down and all functions will return to the default state. As shown in the figure 3.

Figure 3. EN digital interface waveform diagram

#### **Protection**

The JW7952 guarantees robustness with input over-current protection, thermal shutdown, under voltage lockout and input over voltage protection.

# **Input Over-Current Protection**

The JW7952 measures the inductance peak current by top switchs. And the over-current protection threshold is constant 12.5A.

When the inductance peak current exceeds the input over current threshold, the device turns off the top switches and turns on the bottom switches regardless of the status of PWM1 and PWM2 to protect the chip from damaging. When the over current event happens 4 times, IC will enter hiccup mode.

### **Under-Voltage Lockout**

When the  $V_{AVIN}$  falls below the  $V_{AVIN\_UVLO}$  falling threshold, the device stops switching. When the  $V_{AVIN}$  rises above the  $V_{AVIN\_UVLO}$  rising threshold, the device resumes working, if EN is still high.

#### **Input Over-Voltage Protection**

When the  $V_{PVIN}$  rises above the  $V_{PVIN\_OVLO}$  rising threshold, the device stops switching. When the

$V_{PVIN}$  falls below the  $V_{PVIN\_OVLO}$  falling threshold, the device resumes working, if EN is still high and  $V_{AVIN}$  is still above the  $V_{AVIN\_UVLO}$  falling threshold .

#### Thermal Shutdown

When the junction temperature of the JW7952 rises above 150°C, the device enters shut down mode. When the temperature of JW7952 drops below 130°C, the JW7952 can be resumed.

# **PACKAGE OUTLINE**

# **IMPORTANT NOTICE**

Joulwatt Technology Co.,Ltd reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Co.,Ltd does not warrant or accept any liability whatsoever in respect

of any products purchased through unauthorized sales channel.

- JOULWATT TECHNOLOGY CO.,LTD PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, SAFETY INFORMATION AND OTHER RESOURCES, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

Copyright © 2023 JoulWatt

All rights are reserved by Joulwatt Technology Co., Ltd