# 15W Full-Bridge Power Stage with Voltage/Current Demodulation for Highly-Integrated Wireless Power Transmitter

## 1 Descriptions

The SC5008 is a highly integrated analog-front-end that contains all of the analog components required to implement a wireless power transmitter compliant with WPC specifications. The device integrates a full-bridge power stage with low-R<sub>DS(on)</sub> MOSFETs, gate drivers, 5V & 3.3V LDOs, communication demodulators and input current sensing circuit. It can work with a transmitter controller to create a high-performance and cost-effective wireless power transmitter system that complies with both the WPC V1.3.2 Baseline Power Profile (BPP, not more than 5W) and Extended Power Profile (EPP, up to 15W).

The wireless power transmitter system supports foreign object detection (FOD) by continuously monitoring the amount of power transferred and comparing it to the amount of received power, as reported by the power receiver. In order to do this, the SC5008 measures the input DC current very accurately using a current sense amplifier. The built-in 5V and 3.3V LDOs can power both the internal and external circuits. Besides, the SC5008 supports undervoltage lockout (UVLO), over-current & short-circuit protection (OCP & SCP) and over-temperature protection (OTP). The protections significantly enhance the reliability of the whole wireless power transmitter system.

The SC5008 is available in a compact 3mm x 4mm QFN package.

#### 2 Features

- Input voltage range: 3.2V-14V

- Support up to 15W power transfer

- Integrated four 12mohm R<sub>DS(on)</sub> power MOSFETs

- · Integrated FET drivers and bootstrap circuits

- Integrated 5V-100mA and 3.3V-80mA LDOs

- Integrated accurate current sense for FOD

- Integrated voltage and current demodulators

- Compatible with 3.3V and 5V PWM logical signals

- Support various types of power transmitter design in the WPC V1.3.2

- UVLO/OCP/SCP/OTP

- 3mm x 4mm QFN package

## 3 Applications

- WPC Compliant Wireless Power Transmitters

- Proprietary Wireless Power Transmitters

- General Wireless Power Chargers for Consumer,

Industrial and Medical Applications

#### 4 Device Information

| Part Number | Package | Dimension          |

|-------------|---------|--------------------|

| SC5008      | QFN 19  | 3mm x 4mm x 0.75mm |

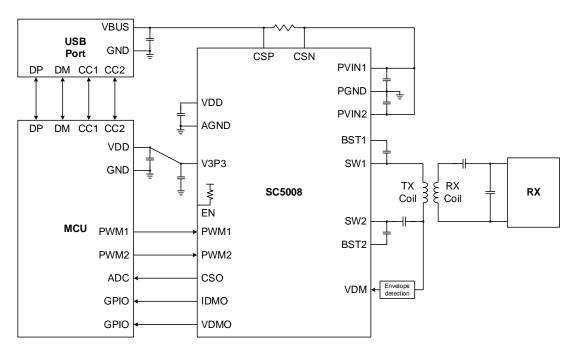

# 5 Typical Application Circuit

1) General Wireless Power Transmitter:

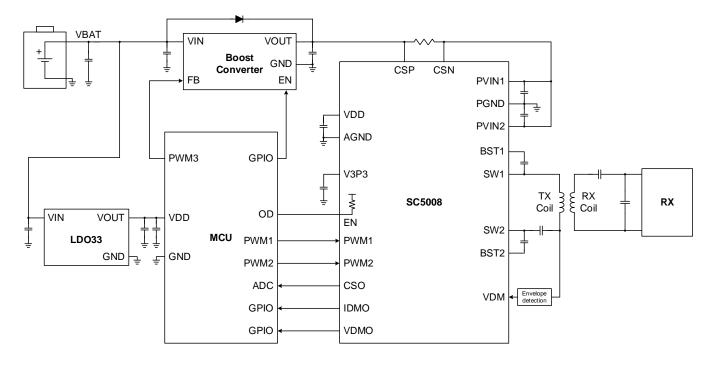

## 2) Wireless Power bank:

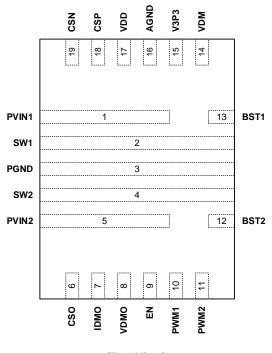

# 6 Terminal Configuration and Functions

(Top View)

| TERMINAL |       |     | DECORIDATION                                                                                                                                                                            |  |

|----------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER   | NAME  | I/O | DESCRIPTION                                                                                                                                                                             |  |

| 1        | PVIN1 | PWR | Input voltage of half-bridge MOSFETs Q1 and Q2. A ceramic capacitor of 22 µF or more is required between this pin and the PGND pin.                                                     |  |

| 2        | SW1   | PWR | Switching node of the half bridge MOSFETs Q1 and Q2.                                                                                                                                    |  |

| 3        | PGND  | PWR | Power ground.                                                                                                                                                                           |  |

| 4        | SW2   | PWR | Switching node of the half bridge MOSFETs Q3 and Q4.                                                                                                                                    |  |

| 5        | PVIN2 | PWR | Input voltage of half-bridge MOSFETs Q3 and Q4. A ceramic capacitor of 22 µF or more is required between this pin and the PGND pin.                                                     |  |

| 6        | cso   | 0   | Current sense amplifier output.                                                                                                                                                         |  |

| 7        | IDMO  | 0   | Output of the demodulated 2-kHz communication signal based on current demodulation scheme.                                                                                              |  |

| 8        | VDMO  | 0   | Output of the demodulated 2-kHz communication signal based on voltage demodulation scheme.                                                                                              |  |

| 9        | EN    | ı   | Enable pin. Logic HIGH enables the IC and logic LOW disables the IC. The EN pin is pulled up internally.                                                                                |  |

| 10       | PWM1  | ı   | PWM logic input for the Q1 and Q2 as shown in the Block Diagram. Logic HIGH turns on the high-side FET Q1 and turns off the low-side FET Q2. Logic LOW turns on the low-side FET Q2 and |  |

|    |      |     | turns off the high-side FET Q1.                                                                                                                                                                                         |

|----|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | PWM2 | ı   | PWM logic input for the Q3 and Q4 as shown in the Block Diagram. Logic HIGH turns on the high-side FET Q3 and turns off the low-side FET Q4. Logic LOW turns on the low-side FET Q4 and turns off the high-side FET Q3. |

| 12 | BST2 | PWR | High-side gate driver bootstrap rail. Connect a 0.1μF ceramic capacitor between the BST2 and SW2 pins.                                                                                                                  |

| 13 | BST1 | PWR | High-side gate driver bootstrap rail. Connect a 0.1µF ceramic capacitor between the BST1 and SW1 pins.                                                                                                                  |

| 14 | VDM  | I   | High-pass filter input. Voltage demodulation pin for data packets based on coil voltage variation.                                                                                                                      |

| 15 | V3P3 | 0   | Output of internal 3.3V LDO to power the controller and other external devices. A ceramic capacitor of 2.2 µF is required between this pin and the AGND pin.                                                            |

| 16 | AGND | -   | Analog ground.                                                                                                                                                                                                          |

| 17 | VDD  | 0   | Output of internal 5V LDO to power internal circuits and external devices. A ceramic capacitor of 2.2 $\mu F$ is required between this pin and the AGND pin.                                                            |

| 18 | CSP  | I   | Positive end of input current sense amplifier.                                                                                                                                                                          |

| 19 | CSN  | I   | Negative end of input current sense amplifier.                                                                                                                                                                          |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                              |                                                 | MIN  | MAX   | UNIT |

|----------------------------------------------|-------------------------------------------------|------|-------|------|

|                                              | PVIN1, PVIN2, CSP, CSN                          | -0.3 | 20    | V    |

|                                              | SW1, SW2                                        | -1   | 20    | V    |

| Voltage range at terminals (2)               | BST1                                            | -0.3 | SW1+5 | V    |

|                                              | BST2                                            | -0.3 | SW2+5 | V    |

|                                              | VDD, V3P3, VDM, CSO, IDMO, VDMO, EN, PWM1, PWM2 | -0.3 | 6.5   | V    |

| Differential Voltage range between terminals | CSP-CSN                                         | -0.6 | 0.6   | V    |

| Temperature Range                            | Operating Junction, T <sub>J</sub>              | -40  | 150   | °C   |

| remperature Nange                            | Storage temperature range, T <sub>stg</sub>     | -65  | 150   | °C   |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 Thermal Information

| THERMAL RESISTANCE | QFN-19 (3mm x 4mm)          | UNIT |      |

|--------------------|-----------------------------|------|------|

| $\Theta_{JA}$      | 47                          | °C/W |      |

| Θ <sub>JC</sub>    | Junction to case resistance | 13   | °C/W |

<sup>(1)</sup> Measured on JESD51-7, 4-layer PCB.

## 7.3 Handling Ratings

| PARAMETER | DEFINITION                                               | MIN   | MAX  | UNIT |

|-----------|----------------------------------------------------------|-------|------|------|

| ESD (1)   | Human body model (HBM) ESD stress voltage <sup>(2)</sup> | -2000 | 2000 | V    |

|           | Charged device model (CDM) ESD stress voltage (3)        | -750  | 750  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

## 7.4 Recommended Operating Conditions

|                                         |                                      | MIN | TYP | MAX | UNIT |

|-----------------------------------------|--------------------------------------|-----|-----|-----|------|

| V <sub>PVIN1</sub> , V <sub>PVIN2</sub> | Input voltage range                  | 3.2 |     | 14  | V    |

| CPVIN1, CPVIN2                          | PVIN1, PVIN2 Ceramic Capacitor       |     | 22  |     | μF   |

| C <sub>BST1</sub> , C <sub>BST2</sub>   | BST1-SW1, BST2-SW2 Ceramic Capacitor |     | 0.1 |     | μF   |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **SC5008 DATASHEET**

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| C <sub>VDD</sub> , C <sub>V3P3</sub> | VDD, V3P3 Ceramic Capacitor    |     | 2.2 |     | μF |

|--------------------------------------|--------------------------------|-----|-----|-----|----|

| T <sub>J</sub>                       | Operating junction temperature | -40 |     | 125 | °C |

## 7.5 Electrical Characteristic

$V_{PVIN1} = V_{PVIN2} = 12V$ , typical values are tested at room temperature, unless otherwise specified.

| PARAMETER            |                                     | TEST CONDITIONS                                | MIN      | TYP  | MAX   | UNIT |

|----------------------|-------------------------------------|------------------------------------------------|----------|------|-------|------|

| SUPPLY V             | OLTAGE                              |                                                |          |      |       |      |

| V <sub>PVIN</sub>    | Operating input voltage             |                                                | 3.2      |      | 14    | V    |

| V                    | I lador voltago logico it throubold | Rising edge                                    |          | 3    |       | V    |

| $V_{IN\_UVLO}$       | Under voltage lockout threshold     | Falling edge                                   |          | 2.7  |       | V    |

| IQ                   | Quiescent current into PVIN         | EN= high, no switching, V <sub>PVIN</sub> =12V |          | 0.95 |       | mA   |

| I <sub>SD</sub>      | Shutdown current into PVIN          | EN =low, V <sub>PVIN</sub> =3.5V               |          | 15   |       | μΑ   |

| VOLTAGE              | REGULATOR (VDD)                     |                                                |          |      |       |      |

| \ /                  | VDDttt                              | $V_{PVIN}$ = 5V, Cout = 2.2 $\mu$ F            |          | 4.8  |       | V    |

| $V_{DD}$             | VDD output voltage                  | V <sub>PVIN</sub> = 12V, Cout = 2.2μF          | 4.85     | 5    | 5.15  | V    |

| \                    | VDD under-voltage lockout           | Rising edge                                    |          | 2.8  |       |      |

| $V_{DD\_UVLO}$       | threshold                           | Falling edge                                   |          | 2.5  |       | V    |

| I <sub>VDD_LIM</sub> | VDD output current capability       | V <sub>PVIN</sub> ≥5V, Cout = 2.2uF            | 100      |      |       | mA   |

| 3.3V LDO             |                                     |                                                |          |      |       |      |

| V <sub>3P3</sub>     | V3P3 output voltage                 | VDD = 5.0V, Cout = 2.2μF                       | 3.201    | 3.3  | 3.399 | V    |

| I <sub>3P3_LIM</sub> | V3P3 output current capability      | VDD = 5.0V, Cout = 2.2uF                       | 80       |      |       | mA   |

| CURRENT              | SENSE AMPLIFIER                     |                                                |          |      |       |      |

| I <sub>PVIN</sub>    | Input current range                 | Sense Resistor=20mohm;<br>VDD = 5.0V           | 0        |      | 3.5   | А    |

| G                    | Gain                                | Sense Resistor=20mohm;<br>Sense Current=2A     | 49       | 50   | 51    | V/V  |

| V <sub>CSO0</sub>    | CSO offset voltage                  | Measured at the CSO pin; $V_{CSP} = V_{CSN}$   |          | 0.5  |       | V    |

| POWER S              | WITCH and DRIVER                    |                                                |          |      |       |      |

|                      | SW1 High-side R <sub>DS(on)</sub>   | V <sub>DD</sub> = 5.0V                         |          | 12   |       | mΩ   |

| Б                    | SW1 Low-side R <sub>DS(on)</sub>    | V <sub>DD</sub> = 5.0V                         |          | 12   |       | mΩ   |

| $R_{DS(on)}$         | SW2 High-side R <sub>DS(on)</sub>   | V <sub>DD</sub> = 5.0V                         |          | 12   |       | mΩ   |

|                      | SW2 Low-side R <sub>DS(on)</sub>    | V <sub>DD</sub> = 5.0V                         |          | 12   |       | mΩ   |

| SHORT CI             | RCUIT PROTECTION                    |                                                |          |      |       |      |

| I <sub>LIM</sub>     | High-side current limit threshold   |                                                |          | 12   |       | Α    |

| Tp                   | Hiccup period                       |                                                |          | 10   |       | ms   |

| CNT <sub>OCP</sub>   | Peak OCP deglitch count             |                                                |          | 4    |       |      |

| EN, PWM              | 1, PWM2                             |                                                |          |      |       |      |

| V <sub>IH</sub>      | Input logic high                    | V3P3=3.3V                                      | 2.65     |      |       | V    |

| V <sub>IL</sub>      | Input logic low                     | V3P3=3.3V                                      |          |      | 0.65  | V    |

| VDMO, ID             | MO                                  | <u> </u>                                       | <u> </u> |      |       | I    |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| V <sub>OH</sub> | Output logic high            |  | 0.9*VDD | V  |  |  |  |

|-----------------|------------------------------|--|---------|----|--|--|--|

| V <sub>OL</sub> | Output logic low             |  | 0.1*VDD | V  |  |  |  |

| THERMAL         | THERMAL SHUTDOWN             |  |         |    |  |  |  |

| T <sub>SD</sub> | Thermal shutdown temperature |  | 160     | °C |  |  |  |

| ISD             | Thermal shutdown hysteresis  |  | 25      | °C |  |  |  |

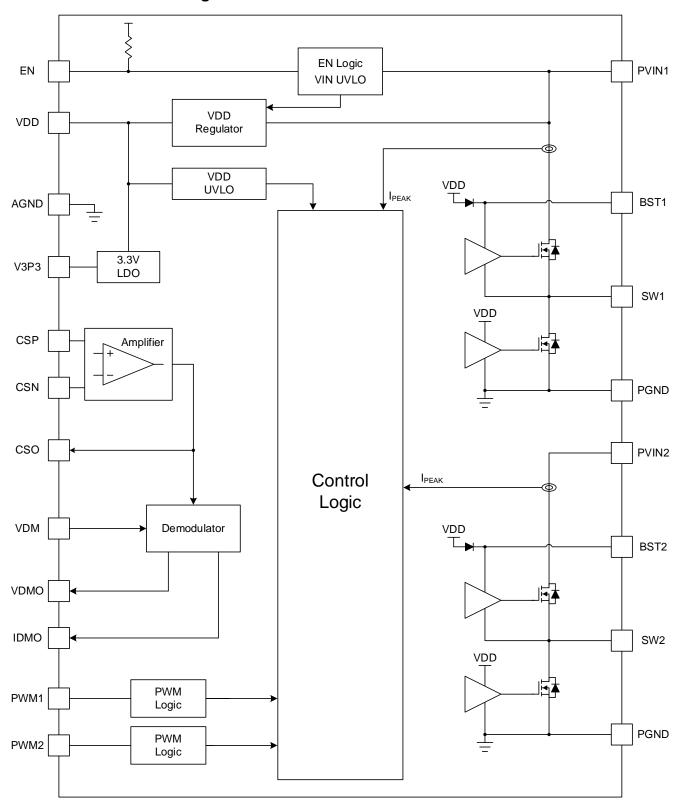

# 8 Functional Block Diagram

## 9 Feature Description

## 9.1 Enable and Start up Logic

The UVLO function protects the chip from operating at insufficient power supply. When the input voltage rises above 3V and the EN pin voltage exceeds the high threshold of 2.65V, the 5V voltage regulator works at once, and also the 3.3V voltage regulator. It should be noted that the EN pin is pulled up internally in the chip. Once the PVIN and VDD voltage exceed their own high threshold, the full-bridge power stage responses to the PWM logic.

When the EN pin is pulled down externally, the chip is disabled, and the shutdown current is about 15uA (typical).

#### 9.2 Current Sense Amplifier

To support foreign object detection (FOD), the SC5008 senses the average input current to the device. The integrated current sense amplifier has a typical voltage gain of 50. For proper scaling of the current signal, the recommended current sense resistor is  $10m\Omega/20m\Omega$ .

The current sense amplifier output has a typical 0.5V offset when the sensed current is zero. For accurate measurement of the input current, MCU need to calibrate this offset.

#### 9.3 PWM Control

The PWM1 input controls the internal MOSFETs Q1 and Q2, and the PWM2 input controls the internal MOSFETs Q3 and Q4 as shown in the Block Diagram. The PWM1 and PWM2 can independently control the SW1 and SW2 duty cycle and frequency. Please be noted that the dead time has already been implemented between Q1 (or Q3) and Q2 (or Q4) internally, so there is no need for dead time between external control signals PWM1 and PWM2.

#### 9.4 Voltage Regulators

The SC5008 has integrated 5V and 3.3V voltage regulators to power internal gate drivers, control circuits and external transmitter controller. The 5V voltage regulator is powered from PVIN and supplies a regulated 5V voltage at the VDD pin. And the 3.3V voltage regulator is powered from VDD and supplies a regulated 3.3V voltage at the V3P3 pin. Decouple the VDD and V3P3 pins with 2.2µF low-ESR ceramic capacitors that are placed close to the IC. The load capability of 5V and 3.3V regulators is about 100mA and 80mA respectively.

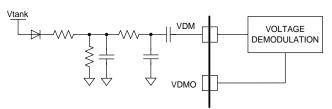

## 9.5 Voltage Demodulation

In order to increase the communication reliability in any load condition, the SC5008 has integrated two demodulation schemes, one based on input peak current information and the other based on coil voltage information. The voltage mode envelope detector is implemented using a discrete solution as depicted on Figure 1. This simple implementation achieves the envelope detector function as well as the DC filter function.

Fig1. Voltage Demodulation

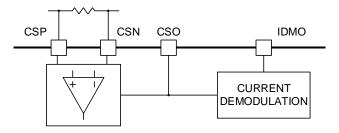

#### 9.6 Current Demodulation

The current-mode detector takes the modulation information from the input peak current. The MCU can detect the demodulation results on VDMO and IDMO pins and then implement the packet decode. It can select either voltage-mode or current-mode signals depending upon which produces the best demodulated signal.

Fig2. Current Demodulation

## 9.7 Over-Current Protection (OCP)

The SC5008 integrates a hiccup-mode-based over-current protection. The currents of the SW1 high-side FET and SW2 high-side FET are sensed and compared to the current-limit threshold during every switching cycle. When the sensed current reaches the current-limit threshold, the over-current fault counter is incremented. If the over-current fault counter reaches 4 and overflows, the high side FETs are turned off and the low side FETs are turned on regardless of the PWM inputs. The IC remains in the hiccup mode for a period equal to 10ms typically and then attempts to restart. The hiccup mode OCP protection can reduce the average current greatly to alleviate the thermal issue and to protect the converter. Once the OCP condition

is removed, the SC5008 exits hiccup mode and goes back to normal operation.

## 9.8 Over Temperature Protection (OTP)

The over temperature protection (OTP) prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 160°C, the SC5008 is shut down. When the temperature drops below threshold (typically 135°C), the chip is enabled again.

## 10 Application Information

## 10.1 Input Current Sense

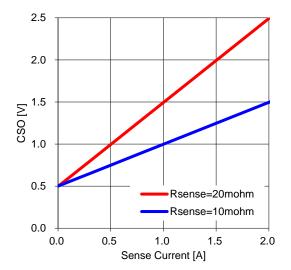

The SC5008 senses the average input current to the device. The recommended current sense resistor is  $10m\Omega/20m\Omega$ . Resistor of 1% or higher accuracy and low temperature coefficient is recommended.

The resistor power rating and temperature coefficient should also be considered. The power dissipation is roughly calculated as P=I<sup>2</sup>R, and I is the highest current flowing through the resistor. The resistor power rating should be higher than the calculated value.

The current sense amplifier output has a typical 0.5V offset when the sensed current is zero. Please be noted that this offset may vary a little from one chip to another, so when MCU is calibrating this offset, it is highly recommended to use ADC to sense this offset instead of using fixed 0.5V.

Figure 3 shows the internal current sense output (CSO) voltage over the sensed current based on different sense resistor. Since the integrated current sense amplifier has voltage gain of 50V/V, if input current is sensed on a  $10m\Omega$  resistor, the voltage to current gain will be 0.5V/A. If input current is sensed on a  $20m\Omega$  resistor, the voltage to current gain will be 1V/A.

#### Fig3. CSO Voltage over Sense Current

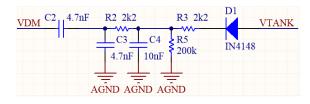

#### 10.2 Voltage/Current Demodulation

The SC5008 simultaneously integrates voltage and current demodulation which are based on coil voltage and input peak current separately. Compared with the discrete demodulation solution, the chip need much less number of external components.

Figure4 shows a typical circuit for voltage demodulation. D1/R3/R5/C4 is an envelope demodulation of the LC tank voltage. R2/C3 is a RC filter which can filter the high frequency switching noise while keep the 2 kHz communication signal. C2 is a DC blocking capacitor which passes through only the ac signal to the internal demodulator.

Fig4. Voltage Demodulation

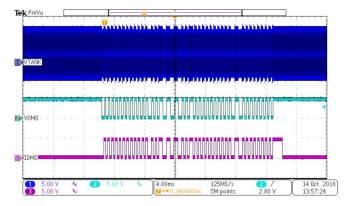

Figure5 shows a typical communication packet, which is composed of a preamble, a header, the actual message, and a checksum, as defined by the WPC standard.

Fig5. VDMO/IDMO Demodulation Outpu

# 11 MECHANICAL DATA

QFN 19 (3mm x 4mm x 0.75mm)